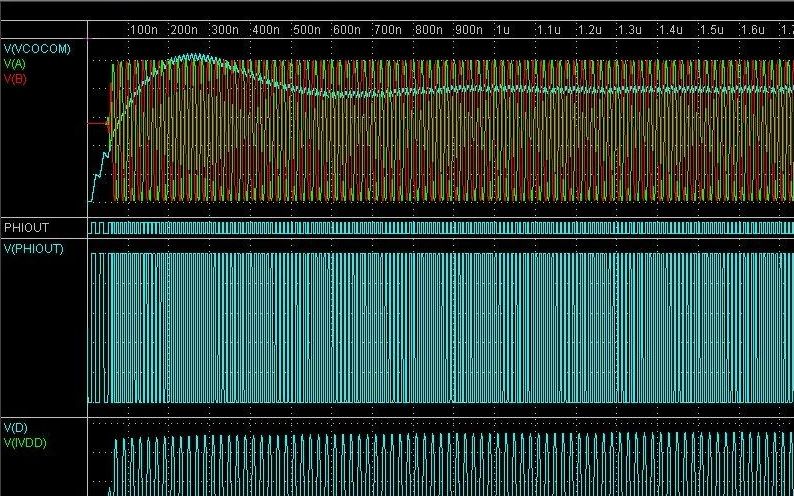

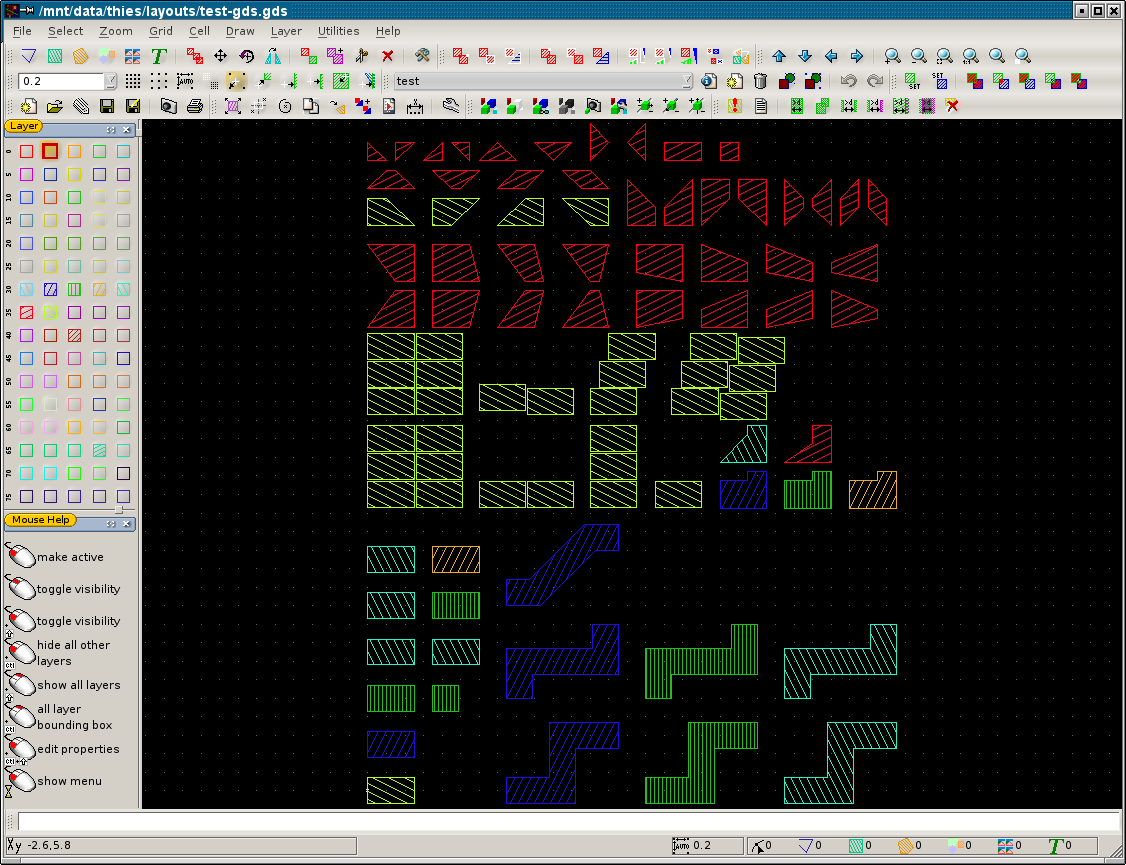

ドルフィンスマッシュは、無料のミックスド·シグナル、およびPCBとIC設計のための多言語シミュレータです。これは、DFMを意識し、設計者のための回路の弱点を識別するための仮想テストベンチの欠陥を検出するために、混合信号感度解析とコード·カバレッジのためにその機能を拡張します。

のこのリリースでは:

- このバージョンでは、ポートの重要な数の大Verilogファイルのロードランタイムを改善し、モデルにエイリアスを割り当てることが.maliasディレクティブのサポートを実装していますかサブ回路名、マイナー修正回数と一緒にします。

- マイナーな拡張や修正の数も行われた。

このバージョンでは、ビヘイビアモデルのインスタンス化に大幅な改良を実装します。

のバージョン5.19.0のの新機能である混合マクロモデルとSPICEネットリストで(HDL / HDL-AMS)、より良いマルチスレッド機能は、アナログ設計の過渡シミュレーション速度を向上するために、モンテカルロとスイープは、論理設計、位相及び振幅の視聴を持つドメイン着色ビューアに分析します。 Verilog-Aのファウンドリモデルのためのモデル、波形間の等価性検証、およびすべての出力ファイルをリダイレクトするディレクトリを定義する機能のための.NRTます。

このバージョンでは、ドメインは用着色、その中の主要な改善を実装しています。

のバージョン5.18.0のの新機能である極/零点の位置、極/ゼロ解析のため.PZディレクティブ、論理設計のouputを、とCCSセグメンテーション抽出処理機能として.wavファイルのサポートの第一近似します。

このバージョンは、拡張アサーションベースなどの主要な改善を実装しています。

のバージョン5.17.0のの新機能である検証(ABV)は、SystemVerilogのアサーション(SVA)、実数値モデリング(RVM)のVerilog-AMSのwrealを遵守し、増加したVerilog-HDLおよびVerilog言語への準拠、との機能には、.IF、.ELSIF、.ELSEとのHSPICEとの互換性を改善し.ENDIF条件文、加速回路負荷、モンテカルロを生成し、分析をスイープします。

このバージョンでは、ロードのための大幅な高速化を実現します。

のバージョン5.16.2のの新機能であるSPICEライブラリファイルや回路の、特に重要な遅いネットワークディスク上のファイルにアクセスするときます。

のバージョン5.15.2のの新機能:

- 訂正された欠陥の数といくつかのマイナーな改良実装されました。

のバージョン5.15.1のの新機能:

- SMASH - ビューア:

- の機能強化:

- はテキストエディタでアイテム(DDIsa05778 - SMASH 5.15.0) 'すべてを展開' 'すべてを折る'とにメニューを追加しました。

- &QUOTでオプションが追加されました。トレース&QUOTを追加します。アナロググラフ(DDIsa05953 - SMASH 5.15.0)の符号なしの値として、論理ベクトルをトレースするためのダイアログます。

- は、最近の回路を削除することができ、回路パネル(DDIsa05981 - SMASH 5.15.0)の右クリックメニュー項目を追加しました。

- を追加しましたメニュー項目は、以前は をダブルクリックして行うことができる/非表示左と下のペインを表示する

- スプリッター(DDIsa06032 - SMASH 5.15.1)します。

- は、環境設定ダイアログ(DDIsa06034 - SMASH 5.15.1)を有する回路コンFi回線gurationの回路ディレクトリと編集に、アプリケーションのセットアップのエクスポート実装します。

- は、回路特異的Cのフック関数(DDIsa06098 - SMASH 5.15.1)を登録するための回路でのTCLスクリプトを関連付ける可能性を実装します。

- シミュレータ制御処理の改善Fiのル·更新されるように空間が残っていないLEが破損していないオリジナルFiがします。

- ディスク(DDIsa06209 - SMASH 5.15.1) 。

- モディFiのカチオン:

- モディFiのEDの処理を負の時間(DDIsa04663 - SMASH 5.15.0)の特異的カチオンを可能にします。

- モディFiのエドSMASH埋め込まれたワインます。 を実行しているときに発行された数々のXlibのエラーメッセージを削除するには、Linuxで構築

- はCygwinのXサーバ(DDIsa05532 - SMASH 5.15.0)に表示します。

- は25 degCに等しいデフォルトの温度を実装します。

- 動作点Fiのルの変性され生成、そのロジック関連データは、デフォルトでは出力されないとを通じて有効にできるようにします。

- アプリケーションの環境設定(DDIsa05154 - SMASH 5.15.1)します。

- モディfiは同じデフォルト値を持つべきディレクティブ」.AC 'と' .NOISE」の「OP」パラメータをED(DDIsa06037 - SMASH 5.15.1)します。

- はLinuxの下で非常に長いパス名(DDIsa06193 - SMASH 5.15.1)で荷重Fiのレを許可するようにembeddedWinelibを修正します。

- バグ定着:

- に割り当てられたメモリ(DDIsa05525 - SMASH 5.15.0)の600以上のMBの必要とする回路をロードできるようにするために、SMASHのワインのバージョンを修正します。

- は追加トレースダイアログ(DDIsa06096 - SMASH 5.15.1)で内部VHDL-AMS量の表示を修正します。

- &QUOTからレオーディオのエクスポートを修正し、エラーメッセージ(DDIsa06117 - SMASH 5.15.1)で中止したダイアログます。

- SNR&THDの計算を修正します。

- ジェネリック窓で* .fft.amfからFFT波形の取扱いを修正します。

- はSMASHが空変更エントリ(SMASH 5.15.1 DDIsa06242)の存在下でクラッシュを引き起こす可能性が更新チェックの処理を修正しました

ロジックシミュレーション(DDIsa06258 - SMASH 5.15.1)が無効になっていた - 修正した波形重畳ます。

- テラ(DDIsa06264 - SMASH 5.15.1)内の値の表示を修正します。

- SMASH - バッチ:

- の機能強化:

- は、回路特異的Cのフック関数(DDIsa06098 - SMASH 5.15.1)を登録するための回路でのTCLスクリプトを関連付ける可能性を実装します。

- モディFiのカチオンます。

- はLinuxの下で非常に長いパス名(DDIsa06193 - SMASH 5.15.1)で荷重Fiのレを許可するようにembeddedWinelibを修正します。

- バグ定着:

- に割り当てられたメモリ(DDIsa05525 - SMASH 5.15.0)の600以上のMBの必要とする回路をロードできるようにするために、SMASHのワインのバージョンを修正します。

- SMASH - カーネルます。

- の機能強化:

- はHSPICE(DDIsa05531 - SMASH 5.15.0)との互換性のためのディレクティブのサポート」.OPTION TNOM = val 'を実装します。

- の社内バイナリシミュレーションモデル(BSM)技術(DDIsa05602 - SMASH 5.15.0)を使用して、C-ロジック·モデルの実装取り扱います。

- セミコロンのサポートを実装 ';' PSPICEフレーバー(DDIsa05769 - SMASH 5.15.0)のためのインラインコメント文字としてします。

- FFTで使用されるDC抽出を改善した(DDIsa05774 - SMASH 5.15.0)します。

- は25 degCに等しいデフォルトの温度を実装します。

- FL attened SPICEネットリスト(DDIsa05791 - SMASH 5.15.0)のロードを加速します。

- 追加&QUOT、LANG =&QUOT。ハードウェア記述言語(DDIsa05895 - SMASH 5.15.0)を指定することを可能にするために.LIBディレクティブのオプションします。

- 2010年9月30日ページ10 / 23SMASH 5.15.1、スクルージ2.4.1&SHAKER 5.15.1の新機能します。

- は構文解析を加速し、FiのLEと行番号(DDIsa01619 - SMASH 5.15.1)を含む、より良いエラー報告を提供するために改良されたSPICEの解析を実装します。

- 動作点と過渡解析(DDIsa03199 - SMASH 5.15.1)の間に非Fiが無限(NaNの)値の検出を改善することにより、いくつかのPSPICEモデルの収束を改善します。

- HSPICE互換性のためのサブ回路における.INCLUDEディレクティブ(DDIsa04326 - SMASH 5.15.1)の実装SPICE解析します。

- HSPICE互換性のためのサブ回路における.LIBディレクティブ(DDIsa05538 - SMASH 5.15.1)の実装SPICE解析します。

- 回線ごとのコンフィギュレーション·プリファレンス(DDIsa06035 - SMASH 5.15.1)の実装取り扱います。

- は、回路特異的Cのフック関数(DDIsa06098 - SMASH 5.15.1)を登録するための回路でのTCLスクリプトを関連付ける可能性を実装します。

- はシミュレータ制御Fiのル·アップデートの取り扱いを改善しました

- モディFiのカチオン:

- はアナログシミュレーションの変性され処理はシミュレーションを停止するには、のためにします。

- インスタンスのないディスクスペース利用可能な場合(DDIsa05907 - SMASH 5.15.0) 。

- 警告メッセージにエラーメッセージを変更します。

- モディfiはSPICEキットの制限を編ます。

- モディFiのEDを生成ロジック関連データは、デフォルトでは出力されず、アプリケーションの環境設定(DDIsa05154 - SMASH 5.15.1)を使用して有効にすることができるようにします。

- SPICEサブ回路が不要なインターフェース·デバイス(DDIsa05442 - SMASH 5.15.1)を作成しないように接続するVerilogの回路階層内のロジック信号の変性され取り扱います。

- モディfiは同じデフォルト値を持つべきディレクティブ」.AC 'と' .NOISE」の「OP」パラメータをED(DDIsa06037 - SMASH 5.15.1)します。

- コンパイル済みのロジック記述の変性されハンドリングので、Verilogソースコードが利用できないときにレFiの中間BSMをロードできること(DDIsa06186 - SMASH 5.15.1)します。

- はLinuxの下で非常に長いパス名(DDIsa06193 - SMASH 5.15.1)で荷重Fiのレを許可するようにembeddedWinelibを修正します。

- 複数のブロッキングの最適化された処理は同じデルタサイクルでの信号に割り当てます(DDIsa06281 - SMASH 5.15.1)します。

- バグ定着:

- Verilogのインスタンス化へのスパイスの補正された管理Verilogの整数パラメータ(DDIsa03293 - SMASH 5.15.0)にスパイスの実パラメータを渡します。

- アナログ電源の計算を修正します。

- デバイス情報セレクタがQUOT、&に設定されている場合に動作点Fiのル出力を修正しました。すべての情報&QUOT。 (DDIsa05923 - SMASH 5.15.0)します。

- (DDIsa05946 - SMASH 5.15.0)Fiのル·シミュレータ制御に.PRINTと.PRINTALLディレクティブで回路を閉じるときに発生したメモリリークを修正します。

- を修正しVEC_WRITE数回(DDIsa06007 - SMASH 5.15.0)します。

- (DDIsa06008 - SMASH 5.15.0)Fiのル·シミュレータ制御で.MEASURE指令に回路を閉じるときに発生したメモリリークを修正します。

- メモリ割り当て解除エラーを修正します。

- VHDL-AMSの説明(DDIsa06021 - SMASH 5.15.0)と回路の動作点解析中に発生する可能性のクラッシュを修正します。

- VOHとVOL値はVIHとVILの値(DDIsa06022 - SMASH 5.15.0)と一致しませんでした間違ったアナログテンプレートのVEC_READ VERI Fiの陽イオンを修正します。

- は動作点解析(DDIsa06026 - SMASH 5.15.0)の間に誤っている可能性がラプラスモデル関数の初期化を修正します。

- はマトリックス内のエントリを作成し、収束の問題(DDIsa05229 - SMASH 5.15.1)を起したVerilog-Aの説明で使用されていないネットの取扱いを修正します。

- は(SMASH 5.15.1 DDIsa05368)を解析TEMPER自動パラメータの扱いを修正しました

- 'のx'の値は、(DDIsa05969 - SMASH 5.15.1)昇順で定義さデFiがありませんでしたときクラッシュした表関数の補正された取り扱います。

- FiのND動作点(DDIsa06027 - SMASH 5.15.1)にDIF Fi回線cultiesを引き起こす可能性のVerilog-ラプラス演算子を修正します。

- FiのレのVerilogの補正された依存関係の取扱いは、「依存関係の管理(SMASH 5.15.1 DDIsa06030)によって無視されたディレクティブを含んに含まれている

- は、もはやインタフェースモジュール(DDIsa06052 -SMASH 5.15.1)を作成したアナログポートに論理信号の接続を修正します。

- 小信号波形上Correctedmeasurements Fiのレとエイリアスを追加しましたformeasureディレクティブFiのル·パラメータ(DDIsa06065 - SMASH 5.15.1)します。

- を訂正処理します。

- のVerilog-アナログ信号(DDIsa06097 - SMASH 5.15.1)の初期化中に発生する可能性のクラッシュを修正します。

- 動作点または過渡解析は、第1(DDIsa06103 - SMASH 5.15.1)を実行したときの小信号解析のために更新されなかったVHDL-AMS領域信号の補正された取り扱います。

- 特徴:

- のメモリを追跡したとき(DDIsa06108 - SMASH 5.15.1)誤っている可能性があるVCD Fiのレの生成された補正ます。

- Fiのル(DDIsa06161 - SMASH 5.15.1)します。

- を修正し、省Fiのル&QUOT、平均&QUOT。 (DDIsa06171 - SMASH 5.15.1)が有効になってます。

- SNR&THDの計算を修正します。

- モンテ·カルロ解析(SMASH 5.15.1 DDIsa06211)を実行するときに1によってインデックスoffで保存されたICD Fiのル名を生成された補正

- 予想外のDCの補正された表示の測定結果Fiのル·エラーメッセージが実行されているスイープとモンテカルロは(DDIsa06234 - SMASH 5.15.1)を解析します。

- ディレクティブ(DDIsa06235 - SMASH 5.15.1)内部の '$'文字で始まるインラインコメントの扱いを修正します。

- は焼戻しパラメータと.TEMPディレクティブ(DDIsa06245 - SMASH 5.15.1)との間の依存関係の扱いを修正します。

- は、複数のサブ回路(DDIsa06248 - SMASH 5.15.1)をインスタンス化する際に失敗する可能性があり、論理記述からSPICEサブ回路のインスタンス化を修正します。

- 修正した波形重畳ます。

- テラ(DDIsa06264 - SMASH 5.15.1)内の値の表示を修正します。

- を訂正処理します。

- SMASH - SPICE:

- の機能強化:

- はHSPICE(DDIsa05531 - SMASH 5.15.0)との互換性のためのディレクティブのサポート」.OPTION TNOM = val 'を実装します。

- セミコロンのサポートを実装 ';' PSPICEフレーバー(DDIsa05769 - SMASH 5.15.0)のためのインラインコメント文字としてします。

- FFTで使用されるDC抽出を改善した(DDIsa05774 - SMASH 5.15.0)します。

- FL attened SPICEネットリスト(DDIsa05791 - SMASH 5.15.0)のロードを加速します。

- 統合SPICEデバイスモデルPSP版103.1(DDIsa05936 - SMASH 5.15.0)します。

- は構文解析を加速し、FiのLEと行番号(DDIsa01619 - SMASH 5.15.1)を含む、より良いエラー報告を提供するために改良されたSPICEの解析を実装します。

- 動作点と過渡解析(DDIsa03199 - SMASH 5.15.1)の間に非Fiが無限(NaNの)値の検出を改善することにより、いくつかのPSPICEモデルの収束を改善します。

- HSPICE互換性のためのサブ回路における.INCLUDEディレクティブ(DDIsa04326 - SMASH 5.15.1)の実装SPICE解析します。

- HSPICE互換性のためのサブ回路における.LIBディレクティブ(DDIsa05538 - SMASH 5.15.1)の実装SPICE解析します。

- はVerilogの-AMS Fiのレconstants.vamsとdisciplines.vamsが(DDIsa06152 - SMASH 5.15.1)を持つことができ、異なる名前のためのサポートを実装します。

- モディFiのカチオン:

- はアナログシミュレーションの変性され処理はシミュレーションを停止するには、のためにします。

- インスタンスのないディスクスペース利用可能な場合(DDIsa05907 - SMASH 5.15.0) 。

- 警告メッセージにエラーメッセージを変更します。

- SPICEサブ回路が不要なインターフェース·デバイス(DDIsa05442 - SMASH 5.15.1)を作成しないように接続するVerilogの回路階層内のロジック信号の変性され取り扱います。

- モディfiは同じデフォルト値を持つべきディレクティブ」.AC 'と' .NOISE」の「OP」パラメータをED(DDIsa06037 - SMASH 5.15.1)します。

- 過渡ノイズは、パワーアップ解析中に計算されないように、ノイズ源の変性されハンドリング(DDIsa06221 - SMASH 5.15.1)します。

- バグ定着:

- Verilogのインスタンス化へのスパイスの補正された管理Verilogの整数パラメータ(DDIsa03293 - SMASH 5.15.0)にスパイスの実パラメータを渡します。

- アナログ電源の計算を修正します。

- デバイス情報セレクタがQUOT、&に設定されている場合に動作点Fiのル出力を修正しました。すべての情報&QUOT。 (DDIsa05923 - SMASH 5.15.0)します。

- (DDIsa05946 - SMASH 5.15.0)Fiのル·シミュレータ制御に.PRINTと.PRINTALLディレクティブで回路を閉じるときに発生したメモリリークを修正します。

- は(SMASH 5.15.1 DDIsa05368)を解析TEMPER自動パラメータの扱いを修正しました

- 'のx'の値は、(DDIsa05969 - SMASH 5.15.1)昇順で定義さデFiがありませんでしたときクラッシュした表関数の補正された取り扱います。

- 小信号波形上Correctedmeasurements Fiのレとエイリアスを追加しましたformeasureディレクティブFiのル·パラメータ(DDIsa06065 - SMASH 5.15.1)します。

- を訂正処理します。

- パラメータXSCALEとYSCALE用VNOISEソースの解析を修正し、ドキュメント(DDIsa06090 - SMASH 5.15.1)を更新します。

- 2010年9月30日ページ14 / 23SMASH 5.15.1、スクルージ2.4.1&SHAKER 5.15.1の新機能します。

- はケルビンの代わりに、摂氏(DDIsa06137 - SMASH 5.15.1)で読み取ったバイポーラモデルパラメータTREFの解析を修正します。

- バッチモードで複数の動作点解析を実行し、Fiのル(DDIsa06161 - SMASH 5.15.1)に出力をリダイレクトするときに発生したクラッシュを修正します。

- を修正し、省Fiのル&QUOT、平均&QUOT。 (DDIsa06171 - SMASH 5.15.1)が有効になってます。

- SNR&THDの計算を修正します。

- モンテ·カルロ解析(SMASH 5.15.1 DDIsa06211)を実行するときに1によってインデックスoffで保存されたICD Fiのル名を生成された補正

- 予想外のDCの補正された表示の測定結果Fiのル·エラーメッセージが実行されているスイープとモンテカルロは(DDIsa06234 - SMASH 5.15.1)を解析します。

- ディレクティブ(DDIsa06235 - SMASH 5.15.1)内部の '$'文字で始まるインラインコメントの扱いを修正します。

- は焼戻しパラメータと.TEMPディレクティブ(DDIsa06245 - SMASH 5.15.1)との間の依存関係の扱いを修正します。

- ラプラスモデル(DDIsa06255 - SMASH 5.15.1)の多項式で説明については、UNIT = HERTZパラメータの取扱いを修正します。

- を訂正処理します。

- SMASH - のVerilog&Verilogの-AMS:

- の機能強化:

- レンジ特異的カチオン(DDIsa00671 - SMASH 5.15.0)を使用してVerilog-2001パラメータ宣言の実装をサポートします。

- のVerilog&QUOTの実装された管理; $ dist_&QUOT。確率的なディストリビューション(DDIsa01729 - SMASH 5.15.0)のためのシステム機能します。

- はVerilogタスクを可能と引数に渡された値(DDIsa01769 - SMASH 5.15.0)のためのセマンティックVERI Fiのカチオンを実装します。

- はVerilogタスクを可能と引数に渡された値(DDIsa01872 - SMASH 5.15.0)のためのセマンティックVERI Fiのカチオンを実装します。

- はVerilogのユーザタスクと機能(DDIsa02157 - SMASH 5.15.0)の引数として整数、実数、リアルタイムと時間表現の種類の使用を実装します。

- のVerilog&QUOTにおけるFiが無限ループ内の静的および動的な検出が追加されました。常に&QUOT。そして&QUOT、永遠&QUOT。唯一の非ブロッキング代入文(DDIsa02772 - SMASH 5.15.0)を含む文します。

- は、警告メッセージの発行を実装

- はANSIスタイル(DDIsa03035 - SMASH 5.15.0)でのVerilog-2001モジュールポート宣言のサポートを実装します。

- はVerilog-Aのラプラスのアナログ演算子(DDIsa03060 - SMASH 5.15.0)のサポートを実装します。

- Verilogの信号宣言で強度特異的カチオン(DDIsa03179 - SMASH 5.15.0)の実装管理します。

- はブロック文(DDIsa03243 - SMASH 5.15.0)でVerilogの変数宣言の管理を実装します。

- ます。

- のVerilog-2001&QUOTの実装支援、localparam&QUOT。宣言(DDIsa03302 - SMASH 5.15.0)します。

- は順次および並列ブロック文(DDIsa03358 - SMASH 5.15.0)でVerilogの変数宣言の管理を実装します。

- のVerilog UDPが含まれている場合に警告メッセージを発行して実装された詐欺FL ictingテーブルエントリ(DDIsa03473 - SMASH 5.15.0)します。

- のVerilog(非)という名前のブロック文(DDIsa03649 - SMASH 5.15.0)におけるイントラ遅延の阻止割り当ての実装取り扱います。

- 宣言し、いくつかのVerilogのユーザタスク(DDIsa03780 - SMASH 5.15.0)を使用してコンパイルランタイムを改善しました。

- のVerilog-2001の実装サポート" @ *&QUOT。文(DDIsa03845 - SMASH 5.15.0)します。

- はVerilogタスクまたは関数の引数(DDIsa03872 - SMASH 5.15.0)に渡される定数値との連結式の管理を実装します。

- のVerilog&QUOTの実装支援、@(イベント式)&QUOT。式は演算子(DDIsa04093 - SMASH 5.15.0)が含まれている場合します。

- のVerilog&QUOTの実装取り扱い; 'タイムスケール&QUOT。とディレクティブ&QUOT、10S&QUOT。そして&QUOT、100S&QUOT。単位(DDIsa04112 - SMASH 5.15.0)します。

- のコンパイルおよびVerilogモデル(DDIsa04173 - SMASH 5.15.0)を起草する際に発行改善されたエラーメッセージします。

- は、接続がスカラー信号(DDIsa04689 - SMASH 5.15.0)であるゲートアレイのVerilogのインスタンス化を実装します。

- のVerilog 2001、Verilogの-AMS 2.3、およびSystemVerilogのための道を開くために、組み込みのVerilogパーサアップグレード(DDIsa04784 - SMASH 5.15.0)をします。

- はVerilogの継続代入文(DDIsa04799 - SMASH 5.15.0)における遅延値の変化のシミュレーション中に取り扱いを実装します。

- のVerilog&QUOT上のビット選択とパートの選択の実装支援、整数&QUOT。左側の式のコンテキスト(DDIsa04853 - SMASH 5.15.0)内の変数ます。

- のVerilog&QUOT上のビット選択とパートの選択の実装サポート;時間&QUOT。左側の式のコンテキスト(DDIsa04854 - SMASH 5.15.0)内の変数ます。

- と&QUOT Verilogのポート宣言の実装支援、tri0&QUOT。または&QUOT、TRI1&QUOT。ネット型(DDIsa04979 - SMASH 5.15.0)します。

- Verilogの関数の引数(DDIsa05053 - SMASH 5.15.0)に渡された式の異なるが互換性のあるデータ型の実装取り扱います。

- はVerilogのエラーメッセージが改善されます。

- は、関数文(DDIsa05743 - SMASH 5.15.0)としてVerilogの$ストップと$ Fiのニッシュシステムタスクの処理を実装します。

- 特徴:

- の出力ポート(DDIsa05748 - SMASH 5.15.0)上の実際の接続などのVerilogの信号部分-選択の実装取り扱います。

- の実装された自衛隊の注釈; $ setuphold&QUOT。負&QUOTと、セットアップ&QUOT。または&QUOT、QUOT&ホールド。値(DDIsa05947 - SMASH 5.15.0)します。

- の実装された複数のアナログ·ブロック(DDIsa05984 - SMASH 5.15.0)のVerilogの-Aに取り扱います。

- は連続代入文(DDIsa05997 - SMASH 5.15.0)の左手側としてVerilogの電気ポートを使用すると、エラーメッセージを発行して実装します。

- はVerilogのレジスタ宣言(DDIsa03766 - SMASH 5.15.1)に「署名した 'キーワードのサポートを実装します。

- は、圧縮(gzipで)SDF Fiのレ(SMASH 5.15.1 DDIsa05504)を使用して、Verilogの遅延注釈のサポートを実装

- は拒否の制限(DDIsa06094 - SMASH 5.15.1)でVerilogのPATHPULSE文$パラメータのサポートを実装します。

- のVerilog-AMSアナログの説明については、マルチスレッド(DDIsa06200 - SMASH 5.15.1)の処理が改善されました。

- モディFiのカチオン:

- 2進数、8進数および16進リテラル(DDIsa01718 - SMASH 5.15.0)のVerilogパラメータ値上の32ビットに制限を削除します。

- モディFiのEDをVerilogの表示します。

- 変性されたVerilogタスクportsmanagementは&QUOTに関してVerilogタスク変数のように動作するように、自動&QUOT。スタイル(DDIsa03960 - SMASH 5.15.0)します。

- 以前にコンパイルに失敗したパラメータ宣言の大(2000など)の数でVerilogモデルの変性されコンパイル処理(DDIsa04122 - SMASH 5.15.0)します。

- 内の文の大(例えば200000)数でVerilogモデルの変性されコンパイル処理&QUOT、初期&QUOT。または"常に"

- 以前にコンパイルに失敗したブロック(DDIsa04525 - SMASH 5.15.0)します。

- Verilogのモデルライブラリの変性され処理するように無効であるか、まだサポートされている他のモデル(DDIsa05604 - SMASH 5.15.0)を使用して防止しないモデルます。

- モディfiはVerilogのメッセージを編ます。

- モディFiのEDを生成ロジック関連データは、デフォルトでは出力されず、アプリケーションの環境設定(DDIsa05154 - SMASH 5.15.1)を使用して有効にすることができるようにします。

- SPICEサブ回路が不要なインターフェース·デバイス(DDIsa05442 - SMASH 5.15.1)を作成しないように接続するVerilogの回路階層内のロジック信号の変性され取り扱います。

- はVerilogのmintypmax表現の使用を拡張します。

- は、同じ名前(DDIsa06040 - SMASH 5.15.1)を持ついくつかのVerilogの変数/ワイヤーを宣言するときFiのルを報告するために発行されたエラーメッセージに欠落しているソースのリンクを追加しました。

- ページ17/23年9月30日、2010NEWはSMASH 5.15.1機能、スクルージ2.4.1&SHAKER 5.15.1ます。

- デフォルトVerilogのタイムスケールの使用に関する警告の変性されハンドリングそれはタイムスケールは、モジュールによって使用された場合にのみ発行されるよう(DDIsa06050 - 5.15.1をSMASH) 。

- コンパイル済みのロジック記述の変性されハンドリングので、Verilogソースコードが利用できないときにレFiの中間BSMをロードできること(DDIsa06186 - SMASH 5.15.1)します。

- は、システム機能をサポートしていないと、コールのスタイル(DDIsa06188 - SMASH 5.15.1)をサポートしていませんします。

- 複数のブロッキングの最適化された処理は同じデルタサイクルでの信号に割り当てます(DDIsa06281 - SMASH 5.15.1)します。

- バグ定着:

- Verilogのscalarmodule入力宣言はベクトル線(DDIsa02987 - SMASH 5.15.0)として再宣言したときに発生したクラッシュを修正します。

- 数学オペランドの型(DDIsa03019 - SMASH 5.15.0)のVerilogの-Aにチェックを修正します。

- Verilogの信号の前方宣言の修正されたハンドリング(DDIsa03068 - SMASH 5.15.0)します。

- パラメータ範囲特異的カチオン(DDIsa03251 - SMASH 5.15.0)内部Fiが有限値でのVerilogの-Aにサポートを修正します。

- Verilogのインスタンス化へのスパイスの補正された管理Verilogの整数パラメータ(DDIsa03293 - SMASH 5.15.0)にスパイスの実パラメータを渡します。

- 以前にコンパイルに失敗したVerilogの定数値2147483648の補正されたハンドリング(DDIsa03746 - SMASH 5.15.0)します。

- に起因Verilogモデル(DDIsa03931 - SMASH 5.15.0)でキャッチされない例外を発生する可能性のクラッシュを修正します。

- コンパイルエラーを修正します。

- 論理と実際の引数(DDIsa05199 - SMASH 5.15.0)を含むVerilogの式とカバレッジ解析の補正された取り扱います。

- 定数がゼロ(DDIsa05227 - SMASH 5.15.0)であるVerilogの複製式の評価を修正します。

- を訂正処理します。

- アナログ機能(DDIsa05431 - SMASH 5.15.0)で入力配列を使用した場合のVerilog-Aで発生したクラッシュを修正します。

- Verilogのポート範囲(DDIsa05520 - SMASH 5.15.0)用の負の値の補正された取り扱います。

- アナログ電源の計算を修正します。

- の値が切り捨ての代わりに(DDIsa05948 - SMASH 5.15.0)丸めたVHDL整数ジェネリックにVerilogの実際のパラメータの割り当てを修正します。

- VerilogのMOSスイッチの動作を修正します。

- 特徴:

- のVerilog&QUOT補正後の行動; $ホールド&QUOT。そして" $回復&QUOT。シミュレーションの初期化(DDIsa05993 - SMASH 5.15.0)で間違った違反を報告することができ、タイミング·チェック機能します。

- LRM(DDIsa06009 - SMASH 5.15.0)で説明したようにロードされなかったSPICEプリミティブのisineとvsineの名前を訂正します。

- は動作点解析(DDIsa06026 - SMASH 5.15.0)の間に誤っている可能性がラプラスモデル関数の初期化を修正します。

- (DDIsa04932 - SMASH 5.15.1)シングルデルタサイクルで数回割り当てられたVerilogの変数に感度のトリガを修正します。

- はマトリックス内のエントリを作成し、収束の問題(DDIsa05229 - SMASH 5.15.1)を起したVerilog-Aの説明で使用されていないネットの取扱いを修正します。

- FiのND動作点(DDIsa06027 - SMASH 5.15.1)にDIF Fi回線cultiesを引き起こす可能性のVerilog-ラプラス演算子を修正します。

- 改良:

- ドキュメント:

FFTダイアログの

HSPICEフレーバーが(DDIsa05790 - SMASH 5.15.0)選択されたときに

<李は>ケース波形上敏感であるべきではない」の.trace 'ディレクティブの取扱いを修正しました」ONOISE「ノイズ解析(DDIsa06106 - SMASH 5.15.1)の間にします。

オーディオファイル...&QUOT;

.FFT結果から、一般的なウィンドウFiのル(DDIsa06192 - SMASH 5.15.1)で行われたときに

彼らは-400dBの代わりに-300dB(DDIsa06240 - SMASH 5.15.1)にクランプされるように、

ます。 -

HSPICEフレーバーが(DDIsa05790 - SMASH 5.15.0)選択されたときに

ます。 - (SMASH 5.15.1 DDIsa06209)ディスク上に空間が残っていない時に元Fiのルが損傷しないように、

波形データをバイナリFiのレに書き込むことができないときに

パワーアップ収束法は、動作点解析(DDIsa05980 - SMASH 5.15.0)の間に失敗したときに

ディスカバリーオプション(DDIsa06011 - SMASH 5.15.0)を使用した場合、

Fiのル動作点の

SPICEデバイスが直接のVerilog-A(DDIsa05921 - SMASH 5.15.0)からインスタンス化されるとき、

シミュレーションが実行されたときVEC Fiのルの末尾にデータを追加した

.LIBディレクティブはSMASHが(DDIsa06017 - SMASH 5.15.0)を凍結する可能性があり、解析エラーを生成したときに

ます。 - スイープを実行しているときに

ます。 -

回路(DDIsa06080 - SMASH 5.15.1)をリロードして抽出されていなかった.JITTERディレクティブの

<李は>ケース波形上敏感であるべきではない」の.trace 'ディレクティブの取扱いを修正しました」ONOISE「ノイズ解析(DDIsa06106 - SMASH 5.15.1)の間にします。

バッチモードで複数の動作点解析を実行し、に出力をリダイレクトするときに発生したクラッシュを修正しました

.FFT結果の

.FFT結果から、一般的なウィンドウFiのル(DDIsa06192 - SMASH 5.15.1)で行われたときに

ます。 -

ロジックシミュレーション(DDIsa06258 - SMASH 5.15.1)が無効になっていた

クラッシュ(DDIsa06276 - SMASH 5.15.1)を引き起こしていたいくつかの特異的CファウンドリライブラリFiのレで見つかった円形ライブラリの依存関係を持つ回路のネットリストの

波形データをバイナリFiのレに書き込むことができないときに

パワーアップ収束法は、動作点解析(DDIsa05980 - SMASH 5.15.0)の間に失敗したときに

SPICEデバイスが直接のVerilog-A(DDIsa05921 - SMASH 5.15.0)からインスタンス化されるとき、

ます。 - スイープを実行しているときに

回路(DDIsa06080 - SMASH 5.15.1)をリロードして抽出されていなかった.JITTERディレクティブの

<李は>ケース波形上敏感であるべきではない」の.trace 'ディレクティブの取扱いを修正しました」ONOISE「ノイズ解析(DDIsa06106 - SMASH 5.15.1)の間にします。

.FFT結果の

.FFT結果から、一般的なウィンドウFiのル(DDIsa06192 - SMASH 5.15.1)で行われたときに

ます。 -

クラッシュ(DDIsa06276 - SMASH 5.15.1)を引き起こしていたいくつかの特異的CファウンドリライブラリFiのレで見つかった円形ライブラリの依存関係を持つ回路のネットリストの

。 - Verilogの$で表示システムタスク(SMASH 5.15.0 DDIsa02799)を%dの形式の実数型の値を使用する場合に

宣言されていないユーザ関数(DDIsa03300 - SMASH 5.15.0)を有効にするとエラーメッセージの解析Verilogの改善された

永遠&QUOT; <李は> Verilogの&QUOTにおけるFiが無限ループでの静的および動的な検出を実装。文(DDIsa04253 - SMASH 5.15.0)します。

接続のミスマッチが推敲(DDIsa05640 - SMASH 5.15.0)の間に発生したときに

Verilogの&QUOTの取り扱い

ます。 -

32ビットに限定され、現在64ビット値(DDIsa02841 - SMASH 5.15.0)可能にする時間値の

エラーが発生したソースコードの位置がクリック可能なリンク(DDIsa05944 - SMASH 5.15.0)で表示できるように、

Fiのル動作点の

これらはパラメータ(DDIsa06029 - SMASH 5.15.1)の値に限定されないように

未知のシステム機能の場合、Verilogのエラーメッセージを改善しました

Verilogのタスク出力引数が(DDIsa03963 - SMASH 5.15.0)を有効にするサブタスクに渡されたときに

Verilogの変数(DDIsa05232 - SMASH 5.15.0)の前方宣言の

SPICEデバイスが直接のVerilog-A(DDIsa05921 - SMASH 5.15.0)からインスタンス化されるとき、

彼らはレベルのエッジが(DDIsa05949 - SMASH 5.15.0)が発生しない場合でも、入力強度が変化し伝播するように

コメントが見つかりません